3 ピンアサイン

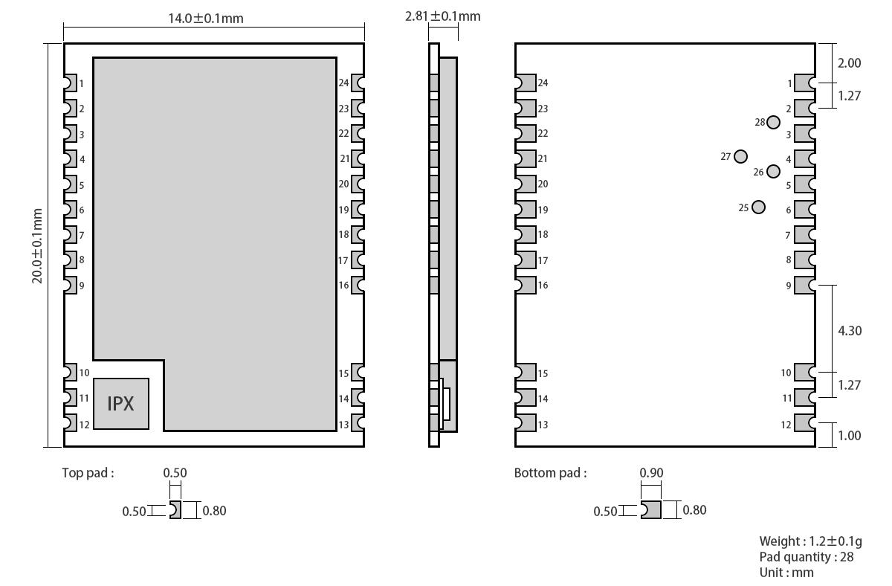

E660-900T22のモジュール外形サイズは、20mm×14mm、厚み2.8mmの端面スルーホール加工を施した、24ピンのDFNモジュールです(図 2)。同一のランドパターンにおいて、リフロー、手はんだ、いずれでも対応できます。

図 2 A660-900T22モジュール外形

背面のテストピン 25、26、27,28は、実装不要です。

背面テストピンのランドを実装する場合は、推奨フットプリントを参考にしてください。

3.1 ピンアウト [A660-900T22]#

| No. | ピン名称 | SoC対応ピン | 方向 | 機能説明 |

|---|---|---|---|---|

| 1 | GND | - | グランド | |

| 2 | VCC | - | 電源供給端子として1.7〜3.7V DCを供給します。 | |

| 3 | SETB | GPIO16 | - | 低電力ウェイクアップピン |

| 4 | DIO1 | GPIO62 | IN/OUT | NC(Reserved) |

| 5 | BUSY | GPIO58 | IN/OUT | NC(Reserved) |

| 6 | I2C_SDA | GPIO15 | IN/OUT | NC(Reserved) |

| 7 | I2C_SCL | GPIO14 | IN/OUT | NC(Reserved) |

| 8 | UART_CTS | GPIO02 | IN/OUT | NC(Reserved) |

| 9 | UART_RTS | GPIO03 | IN/OUT | NC(Reserved) |

| 10 | AGND | - | RFグランド | |

| 11 | ANT | - | アンテナ接続端子 | |

| 12 | AGND | - | RFグランド | |

| 13 | AGND | - | RFグランド | |

| 14 | AGND | - | RFグランド | |

| 15 | AGND | - | RFグランド | |

| 16 | XRES | RSTN_PIN | IN | 外部リセットピン |

| 17 | ADC_IN | GPIO04 | IN | NC(Reserved) |

| 18 | AUX | GPIO44 | IN/OUT | NC(Reserved) |

| 19 | SETA | GPIO33 | IN/OUT | NC(Reserved) |

| 20 | UART_RX | GPIO60 | IN/OUT | UART RX |

| 21 | UART_TX | GPIO17 | IN/OUT | UART TX |

| 22 | SWD_DATA | GPIO06 | IN/OUT | SWD Data |

| 23 | SWD_CLK | GPIO07 | IN/OUT | SWD Clock |

| 24 | GND | - | グランド | |

| 25 | SPI_MISO | GPIO10 | IN/OUT | NC、SPI MISOテストピンで内部にて配線されており、外部端子としては使用できません |

| 26 | SPI_NSS | GPIO09 | IN/OUT | NC、SPI NSSテストピンで内部にて配線されており、外部端子としては使用できません |

| 27 | SPI_MOSI | GPIO11 | IN/OUT | NC、SPI MOSIテストピンで内部にて配線されており、外部端子としては使用できません |

| 28 | SPI_SCK | GPIO08 | IN/OUT | NC、SPI SCKテストピンで内部にて配線されており、外部端子としては使用できません |

3.2 回路設計や基板実装時のピンアサインの注意#

各ピンの取り扱いや制限について、以下注意事項を遵守してください。

XRESリセットピンは、本LoRaWANモジュールを外部から再起動するための機能を提供します。このピンはアクティブ・ロー論理で動作し、ローレベルが印加されるとモジュールの再起動が開始されます。内部プルアップされており、通常動作時は開放または3.3Vにプルアップしてください。